# Module I: Energy Band Theory, Charge Carriers in Semiconductors:

# **Crystalline and Non-crystalline solids:**

This can be subdivided into two states-solid and fluid, of which the later is subdivided into liquid and gaseous state. It can also be subdivided into condensed stated and gaseous state where condensed state is subdivided into the solid and liquid state. Although very little of the matter in the universe is in the solid state, solids constitute much of the physical world around us and a large part of the modern technology is based on the special characteristics of the various solid materials.

# Crystalline and non-crystalline (Amorphous Solids):

Nature favors the crystalline state of the solids, because the energy of the ordered atomic arrangement is lower than that of an irregular packing of atoms.

## **Crystalline Solids:**

A solid in general is said to be a crystal if the constituent particles (atoms, ions or molecules) are arranged in a three dimensional periodic manner or simply it has a reticular structure. In crystalline solids the atoms are stacked in a regular manner, forming a 3-D pattern which may be obtained by a 3-D repetition of a certain pattern unit. It has long-range orderness and thus has definite properties such a sharp melting point. Thus we can say, crystal is a three dimensional periodic array of atoms. When the crystal grows under constant environment, the external geometrical shape of the crystal often remains unchanged. Thus, the shape is a consequence of the internal arrangement of constituent particles. The ideal crystal has an infinite 3D repetition of identical units, which may be atoms or molecules. All ionic solids and most covalent solids are crystalline. All solid metals, under normal circumstances, are crystalline.

## Single crystal:

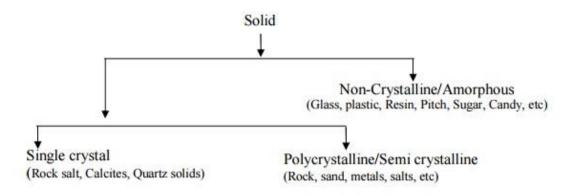

Solid Non-Crystalline/Amorphous (Glass, plastic, Resin, Pitch, Sugar, Candy, etc) Single crystal (Rock salt, Calcites, Quartz solids) Polycrystalline/Semi crystalline (Rock, sand, metals, salts, etc) Crystalline and Non-crystalline solids 2 When the periodicity in crystal pattern extends throughout a certain piece of materials, one speaks of a single crystal or unit crystal or mono-crystal. Rock salt, calcites, quartz, etc. are examples of common single crystal.

# **Polycrystalline solids (Polymorphism):**

When the periodicity in the crystal structure is interrupted at so-called grain boundaries, the crystal is said to be polycrystalline. In this case the size of the grains or crytallites is smaller than the size of the pattern unit which forms the periodicity. The size of the grain in which the structure is periodic may vary from macroscopic dimensions to several angstroms. In general, the grains in such a solid are not related in shape to the crystal structure, the surface being random in shape rather than well defined crystal planes. Rock, sand, metals, salts, etc. are some examples of polycrystalline solids.

#### **Noncrystalline solids:**

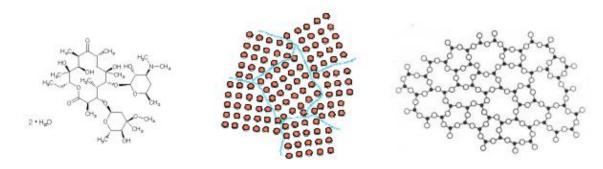

It is the opposite extreme of a single crystal. These types of solids have neither reticular nor granular structure. At most causes exhibit short range orderness in their structure. Glass and plastic are common example of this class. When the size of the grains or crystallites becomes comparable to the size of the pattern unit, we speak of amorphous substances. A typical feature of these substances is that they have no definite melting points. As their temperature is increased, they gradually become soft; their viscosity drops, and begins to behave like ordinary viscous liquids. Amorphous solids have no long-range order. The atoms or molecules in these solids are not periodically located over large distances. An amorphous structure is shown below.

Figure 2: Different crystal structures[1]

Many amorphous materials have internal structures similar to liquids. In fact, the only obvious distinction between amorphous materials, such as glass, and liquids is the high viscosity (resistance to flow) of the amorphous solids. All solids tend to exist in the crystalline state rather than the amorphous state because the crystalline structure always has a larger binding energy. However, in numerous instances amorphous solids are formed when liquids are cooled below the melting temperature.

This occurs for two reasons:

- 1) The structure of the molecules is so complex that they cannot easily rearrange themselves to form a crystalline structure, and/or

- 2) The solid forms so rapidly that the atoms or molecules do not have time enough to rearrange themselves in a crystalline structure.

Generally, amorphous solids have one of two distinct atomic arrangements: either a tangled mass of long-chained molecules or a 3-dimentional network of atoms with no long-range order. Amorphous materials with long-chained molecules (e.g. polymers) have a structure similar to that shown below.

Figure 3:arrangement of molecules for two different materials[1]

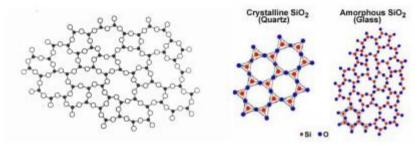

Each segment in above figure represents one of the repeating units of the polymer chain. The arrangement of the molecules is fairly random, resulting in a loosely packed structure. Network amorphous solids are usually Oxides, the most common being Silica (SiO2). The amorphous SiO2 structure is also shown above. Only oxygen atoms are shown (corners of tetrahedral) in this amorphous SiO2 structure. There is a Silicon atom at the center of each tetrahedral which is not shown here. This structure has short-range order but none of the long-range order found in crystalline Silica. Thus, in both amorphous and crystalline Silica, each Silicon atom and each Oxygen atom have essentially the same local surroundings, even though there is no long-range periodicity in the amorphous structure.

Solids that do not have long range atomic order are called amorphous solids. They often have subunits that have consistent form, but their long-range order is disturbed because the sub-units pack randomly. Amorphous solids are formed when liquids are cooled too quickly from the molten state to allow the sub-units to arrange themselves in the low energy, crystalline state. Solids with pure ionic bonds do not form amorphous solids but all the other bond types can produce amorphous solids. Silica (SiO2) can form either covalent amorphous solids, usually called glasses or regular crystal structures (Quartz).

# **Crystal Planes and Miller Indices:**

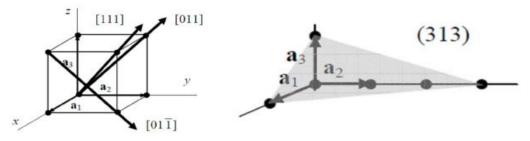

Index system for crystal directions and planes Crystal directions: The direction is specified by the three integers [n1n2n3]. If the numbers n1n2n3 have a common factor, this factor is removed. For example, [111] is used rather than [222], or [100], rather than [400]. When we speak about directions, we mean a whole set of parallel lines, which are equivalent due to transnational symmetry. Opposite orientation is denoted by the negative sign over a number. For example:

Figure 4: Crystal planes

## **Crystal planes:**

The orientation of a plane in a lattice is specified by Miller indices. They are defined as follows. We find intercept of the plane with the axes along the primitive translation vectors a1, a2 and a3. Let's these intercepts be x, y, and z, so that x is fractional multiple of a1, y is a fractional multiple of a2 and z is a fractional multiple of a3. Therefore we can measure x, y, and z in units a1, a2 and a3 respectively. We have then a triplet of integers (x y z). Then we invert it (1/x 1/y 1/z) and reduce this set to a similar one having the smallest integers by multiplying by a common factor. This set is called Miller indices of the plane (hkl). For example, if the plane intercepts x, y, and z in points 1, 3, and 1, the index of this plane will be (313). The orientation of a crystal plane is determined by three points in the plane, provided they are not collinear. If each point lay on a different crystal axis, the plane could be specified by giving the coordinates of the points in terms of the lattice constants a, b, c. A notation conventionally used to describe lattice points (sites), directions and planes is known as Miller Indices. A crystal lattice may be considered as an assembly of equidistant parallel planes passing through the lattice points and are called lattice planes. In order to specify the orientation one employs the so called Miller indices. For simplicity, let us start with a two dimensional lattice and then generalized to three dimensional case. The equation of plane in 2-D and 3D having the intercepts a, b and a, b, c respectively are

$$(x/a) + (y/b) = 1$$

And

$(x/a) + (y/b) + (z/c) = 1$

Crystal direction is the direction (line) of axes or line from the origin and denoted as [111], [100], [010] etc.

# **Schrodinger Wave Equation:**

The free electron model gives us a good insight into many properties of metals, such as the heat capacity, thermal conductivity and electrical conductivity. However, this model fails to help us other important properties. For example, it does not predict the difference between metals, semiconductors and insulators. It does not explain the occurrence of positive values of the Hall coefficient. Also the relation between conduction electrons in the metal and the number of valence electrons in free atoms is not always correct. We need a more accurate theory, which would be able to answer these questions. The problem of electrons in a solid is in general a many-electron problem. The full Hamiltoniam of the solid contains not only the one-electron potentials describing the interactions of the electrons with atomic nuclei, but also pair potentials describing the electron-electron interactions. The many-electron problem is impossible to solve exactly and therefore we need simplified assumptions. The simplest approach we have already considered, it is a free electron model. The next step in building the complexity is to consider an independent electron approximation, assuming that all the interactions are described by an effective potential. One of the most important properties of this potential is that it is periodic on a lattice

$$U(r) = U(r+T) \tag{1}$$

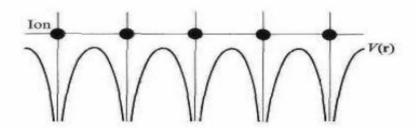

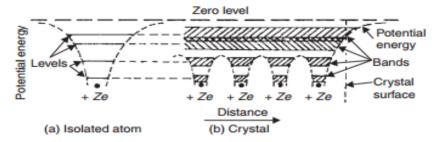

where T is a lattice vector. Qualitatively, a typical crystalline potential might be expected to have a form shown in Fig.1, resembling the individual atomic potentials as the ion is approached closely and flattening off in the region between ions.

Figure 5: The crystal potential seen by the electron

Within the approximation of non-interacting electrons the electronic properties of a solid can be examined by Schrödinger equation

$$\left[ -\frac{\hbar^2}{2m} \nabla^2 + U(\mathbf{r}) \right] \psi(\mathbf{r}) = E \psi(\mathbf{r})$$

(2)

in which  $\psi$  (r) is a wave function for one electron. Independent electrons, which obey a one electron Schrödinger equation (2) with a periodic potential, are known as Bloch electrons, in contrast to "free electrons," to which Bloch electrons reduce when the periodic potential is identically zero.

Now we discuss general properties of the solution of the Schrödinger equation (2) taking into account periodicity of the effective potential (1) and discuss main properties of Bloch electrons, which follow from this solution. We represent the solution as an expansion over plain waves:

$$\psi(\mathbf{r}) = \sum_{\mathbf{k}} c_{\mathbf{k}} e^{i\mathbf{k}\mathbf{r}}$$

(3)

This expansion in a Fourier series is a natural generalization of the free-electron solution for a zero potential. The summation in (3) is performed over all k vectors, which are permitted by the periodic boundary conditions. According to these conditions the wave function (3) should satisfy

$$\psi(x, y,z) = \psi(x + L, y,z) = \psi(x, y + L,z) = \psi(x, y,z + L)$$

(4)

so that

$$k_{x} = \frac{2\pi n_{x}}{L}; \quad k_{y} = \frac{2\pi n_{y}}{L}; \quad k_{z} = \frac{2\pi n_{z}}{L}$$

(5)

where nx, ny, and nz are positive or negative integers. Note that in general  $\psi$  (r) is not periodic in the lattice translation vectors. On the other hand, according to Eq.(1) the potential energy is periodic, i.e. it is invariant under a crystal lattice translation. Therefore, its plane wave expansion will only contain plane waves with the periodicity of the lattice. Therefore, only reciprocal lattice vectors are left in the Fourier expansion for the potential:

$$U(\mathbf{r}) = \sum_{\mathbf{G}} U_{\mathbf{G}} e^{i\mathbf{G}\mathbf{r}} \,, \tag{6}$$

where the Fourier coefficients UG are related to U(r) by

$$U_{G} = \frac{1}{V_{c}} \int_{cell} e^{-i\mathbf{G}\mathbf{r}} U(\mathbf{r}) d\mathbf{r}$$

(7)

where Vc is the volume of the unit cell. It is easy to see that indeed the potential energy represented by (6) is periodic in the lattice:

$$U(\mathbf{r} + \mathbf{T}) = \sum_{\mathbf{G}} U_{\mathbf{G}} e^{i\mathbf{G}(\mathbf{r} + \mathbf{T})} = e^{i\mathbf{G}\mathbf{T}} \sum_{\mathbf{G}} U_{\mathbf{G}} e^{i\mathbf{G}\mathbf{r}} = U(\mathbf{r})$$

(8)

where the last equation comes from the definition of the reciprocal lattice vectors eiGT=1. The values of Fourier components UG for actual crystal potentials tend to decrease rapidly with increasing magnitude of G. For example, for a Coulomb potential UG decreases as 1/G2. Note that since the potential energy is real the Fourier components should satisfy U-G=U\*G.

We now substitute (3) and (6) in Eq.(2) and obtain:

$$\frac{\hbar^2}{2m} \sum_{\mathbf{k}} k^2 c_{\mathbf{k}} e^{i\mathbf{k}\mathbf{r}} + \sum_{\mathbf{k}} \sum_{\mathbf{G}} U_{\mathbf{G}} c_{\mathbf{k}} e^{i(\mathbf{k}+\mathbf{G})\mathbf{r}} = E \sum_{\mathbf{k}} c_{\mathbf{k}} e^{i\mathbf{k}\mathbf{r}}$$

(9)

Changing the summation index in the second sum on the left from k to k+G this equation can be rewritten in a form:

$$\sum_{\mathbf{k}} e^{i\mathbf{k}\mathbf{r}} \left\{ \left( \frac{\hbar^2}{2m} k^2 - E \right) c_{\mathbf{k}} + \sum_{\mathbf{G}} U_{\mathbf{G}} c_{\mathbf{k} - \mathbf{G}} \right\} = 0$$

(10)

Since this equation must be satisfied for any r the Fourier coefficients in each separate term of (10) must vanish and therefore

$$\left(\frac{\hbar^2}{2m}k^2 - E\right)c_k + \sum_{\mathbf{G}}U_{\mathbf{G}}c_{\mathbf{k}-\mathbf{G}} = 0$$

(11)

This is a set of linear equations for the coefficients ck. These equations are nothing but restatement of the original Schrödinger equation in the momentum space, simplified by the fact that the potential is periodic. This set of equations does not look very pleasant because, in principle, an infinite number of coefficients should be determined. However, a careful examination of Eq.(11) leads to important consequences.

First, we see that for a fixed value of k the set of equations (11) couples only those coefficients, whose wave vectors differ from k by a reciprocal lattice vector. In the one-dimensional case these are k,  $k\pm 2\pi/a$ ,  $k\pm 4\pi/a$ , and so on. We can therefore assume that the k vector belongs to the first Brillouin zone. The original problem is decoupled to N independent problems (N is the total number of atoms in a lattice): for each allowed value of k in the first Brillouin zone. Each such problem has solutions that are superposition of plane waves containing only the wave vector k and wave vectors differing from k by the reciprocal lattice vector. Putting this information back into the expansion (3) of the wave function  $\psi$  (r), we see that the wave function will be of the form

$$\psi_{\mathbf{k}}(\mathbf{r}) = \sum_{\mathbf{G}} c_{\mathbf{k}-\mathbf{G}} e^{i(\mathbf{k}-\mathbf{G})\mathbf{r}}$$

(12)

where the summation is performed over the reciprocal lattice vectors and we introduced index k for the wave function. We can rearrange this so that

$$\psi_{\mathbf{k}}(\mathbf{r}) = e^{i\mathbf{k}\mathbf{r}} \sum_{\mathbf{G}} c_{\mathbf{k}-\mathbf{G}} e^{-i\mathbf{G}\mathbf{r}}$$

(13)

Or

$$\psi_{\mathbf{k}}(\mathbf{r}) = e^{i\mathbf{k}\mathbf{r}} u_{\mathbf{k}}(\mathbf{r}) \tag{14}$$

where uk(r)=uk(r+T) is a periodic function which is defined by

$$u_{\mathbf{k}}(\mathbf{r}) = \sum_{\mathbf{G}} c_{\mathbf{k}-\mathbf{G}} e^{-i\mathbf{G}\mathbf{r}}$$

(15)

Equation (14) is known as Bloch theorem, which plays an important role in electronic band structure theory.

## **Kronig-Penney Model:**

The fundamental nature of insulators, conductors and semiconductors can be functionally explained based on band theory. The recent development in semiconductor physics, the semiconductor hetero-structures are also analyzed using the concept of band theory. Another notable theory, the free-electron theory, can help in understanding the electron movement in metals. It assumes that, the valence electron in a metal absorbs thermal energy which ultimately is converted into kinetic energy with an average of (3/2)KBT based on law of equipartition of energy. But the calculated molar electronic specific heat does not match with the experimental value. Hence it can be concluded that the equipartition law and the classical MaxwellBoltzmann statistics are not adequate for evaluating electronic specific heat in metals. Another failure of classical free electron theory is that, it does not account for the magnetic moment of electron due to its spin.

The free-electron theory, which neglects the magnetic moment of electrons arising from their spin predicts that, paramagnetic susceptibility is proportional to the temperature for each electron. On the contrary, the experimental results show that the susceptibility is almost independent (constant) of temperature. The reason is, the classical theory allows all the free electrons to gain energy which does not actually happen in reality, which leads to drastic difference between the calculated and the observe values. At this juncture, the quantum free-electron theory steps in, assumes that an electron in a metal experiences a constant or zero potential and hence is free to move within the lattice. The quantum free-electron theory thus successfully explains the specific heat, electrical conductivity, thermionic emission, thermal conductivity and para magnetism of materials. However, the concept fails to differentiate the conductivities in conductors, semiconductors and insulators. In a real crystal, electrons move in a regularly arranged lattice of positive ions. The electrons have the zero potential at the positive ion site and possess maximum value at the intermediate lattice points. This could be schematically represented as shown in Fig. 2(sine wave notation). The observed potential is periodical as the lattice planes. Bloch has the solution as  $\psi(x) = Uk(x)e$  ikx for the Schrödinger equation, which describes the electron motion:

$$\frac{d^2\psi}{dx^2} + \frac{2m}{\hbar^2} [E - V(x)]\psi = 0$$

where,  $\psi$  is the wave function and Uk(x) in the Bloch's solution, which has the periodicity of the lattice. Hence, the wave function includes both a plane wave eikx which is modulated by the periodic function Uk(x) and the state of motion of electron, which is represented by the wave vector k. However, it is difficult (not tractable) to solve the Schrödinger's equation with the sinusoidal periodicity. Therefore, Kronig and Penney suggested a simpler model, where the inner potential of the crystal system has the rectangular shaped potential.

Thus, in the Kronig Penney model, instead of experiencing a gradual variation in the strength of the potential electrons experience a maximum potential (potential well) and minimum value (potential barrier) in the presence of the lattice planes.

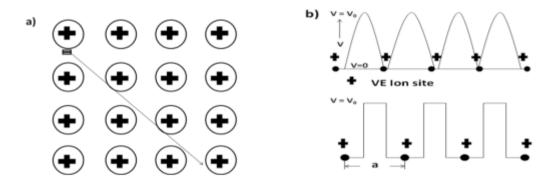

Figure 6: One dimensional periodic potential distribution for a crystal

Figure 7: Brillouin zone

We construct the first Brillouin zone from the shortest lattice vector  $G_1$  as follows. We construct the second Brillouin zone from the next shortest vector  $G_2$  and so on.

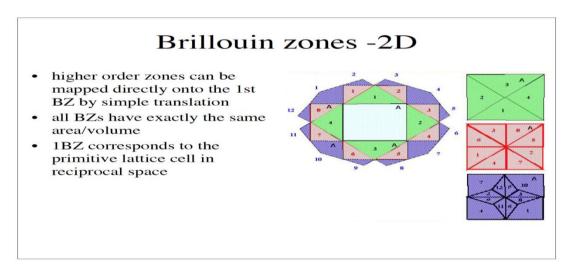

# Brillouin Zones- 2D

Figure 8: Brillouin zone

#### construction

- Reciprocal lattice

- Bisect vectors to the nearest neighbors

- Area defined by bisecting lines represents 1BZ

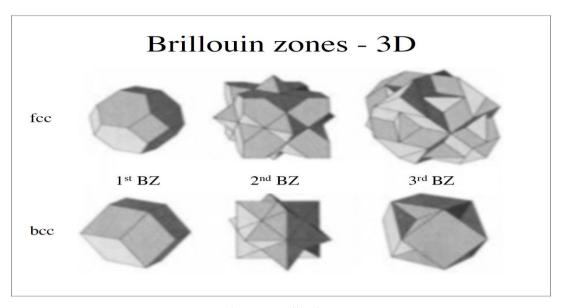

# Three Dimensional Brillouin Zones:

- A 3-dimensional Brillouin zone can be constructed in a similar way by bisecting all lattice vectors and placing planes perpendicular to these points of bisection.

- This is similar to the Wigner Seitz cell in the real lattice.

# Wigner Seitz Cell:

- A primitive unit cell which shows the cubic symmetry of the lattice( for the cubic system).(real lattice)

- The First Brillouin zone is the Wigner Seitz cell in the reciprocal lattice

Figure 9 : Brillouin zone

Lets Study These Figures:

- \*First Brillouin zone of the bcc structure

- ⇒Free electron bands for bcc structure

- \*First Brillouin zone of the fcc structure

- ⇒Free electron bands for fcc structure

•

#### Explanation of these symbols:

Look between the graph of bands and the first Brillouin zone, you will find:

$\Gamma$ : center of the Brillouin zone

X: [100]intercept

K: [110]intercept

$L{:}\left[111\right] intercept$

$\Gamma$  – X: path  $\Delta$

$\Gamma$  – L: path  $\Lambda$

$\Gamma$  – K: path  $\Sigma$

## Number of states in the band:

In solid-state and condensed matter physics, the density of states (DOS) of a system describes the number of states per interval of energy at each energy level that are available to be occupied.

# Band gap in the nearly free electron model:

Having derived Bloch's theorem we are now at a stage where we can start introducing the concept of bandstructure. When someone refers to the bandstructure of a crystal they are generally talking about its electronic dispersion, E(k) (i.e. how the energy of an electron varies as a function of crystal wavevector). However, Bloch's theorem is very general and can be applied to any periodic interaction, not just to electrons in the periodic electric potential of ions. For example in recent years the power of band theory has been applied to photons in periodic dielectric media to study photonic bandstructure (i.e. dispersion relations for photons in a "photonic crystal"). In this lecture we will firstly take a look at dispersion for an electron in a periodic potential where the potential very weak (the nearly free electron approximation) and in the next lecture we will look at the case where the potential is very strong (tight binding approximation). Firstly let's take a closer look at dispersion.

You will recall from the Sommerfeld model that the dispersion of a free electron is  $E(k) = (h^- 2k \ 2)/(2m)$ . It is completely isotropic (hence the dispersion only depends on k = |k|) and the Sommerfeld model produces exactly this band structure for every material – not very exciting! Now we want to understand how this parabolic relation changes when you consider the periodicity of the lattice. Using Bloch's theorem you can show that translational symmetry in real space (characterised by the set translation vectors  $\{T\}$ ) leads to translational symmetry in k-space (characterised by the set of reciprocal lattice vectors  $\{G\}$ ). Knowing this we can take another look at Schr"odinger's equation for a free electron in a periodic potential V(r):

$$H\psi_{\nu \mathbf{k}}(\mathbf{r}) = \{-\frac{\hbar^2 \nabla^2}{2m} + V(\mathbf{r})\}\psi_{\nu \mathbf{k}}(\mathbf{r}) = E_{\nu \mathbf{k}}\psi_{\nu \mathbf{k}}(\mathbf{r})$$

and taking the limit  $V(r) \rightarrow 0$  we know that we have a plane wave solution. This implies that the Bloch function  $u(r) \rightarrow 1$ . However considering the translational invariance in k-space the dispersion relation must satisfy:

$$E_{\nu\mathbf{k}} = \frac{\hbar^2 |\mathbf{k}|^2}{2m} = \frac{\hbar^2 |\mathbf{k} + \mathbf{G}|^2}{2m}$$

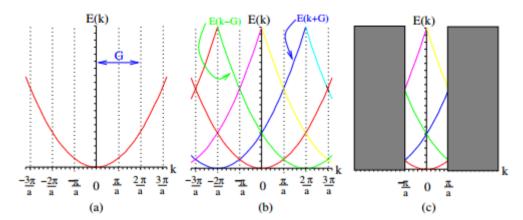

for the set of all reciprocal lattice vectors {G}. This dispersion relation is show in Figure 10.

Figure 10: Simple bandstructure diagrams for a one dimensional periodic solid in the limit  $V(r) \rightarrow 0$  expressed in the extended zone (a), repeated zone (b), and reduced zone (c) schemes.

Since we are in the weak potential limit we can treat the crystal potential as a weak perturbation added to the Hamiltonian of a free electron. Let's start with the Schr odinger equation for a free electron

$H^{\circ}$  owvk(r) = Evkwvk(r)

Where

$H^{\circ} o = p^2/(2m)$

which has plane wave eigenstates

$$\psi_{i,\mathbf{k}}(\mathbf{r}) = \frac{1}{\sqrt{V_{r3}}} \exp(i\mathbf{k} \cdot \mathbf{r})$$

We now introduce a small perturbation, H<sup>0</sup> associated with the crystal potential

$$\hat{H} = \hat{H}_0 + \hat{H}'$$

Since the lattice is periodic we may expand the perturbation into a Fourier series where {G} are a set of vectors and VG are Fourier coefficients

$$\hat{H}' = V(\mathbf{r}) = \sum_{\{G\}} V_G \exp(-i\mathbf{G} \cdot \mathbf{r})$$

Since the lattice is periodic we may expand the perturbation into a Fourier series where G are a set of vectors and VG are Fourier coefficients.

# **Tight binding model:**

Solution of the tight binding model is periodic in k. Apparently have an infinite number of k states for each allowed

In fact the different k states all equivalent Bloch States

$$\psi(\mathbf{r} + \mathbf{R}) \equiv e^{i\mathbf{k}\cdot\mathbf{R}}\psi(\mathbf{r})$$

Let k = k' + G where k' is in the first Brillouin zone and G is a rec iproca l latt ice vector.

$$\psi(\boldsymbol{r}+\boldsymbol{R})\equiv e^{ik'.R}e^{iG.R}\psi(\boldsymbol{r})$$

But G.R =  $2 \pi$  n, n-integer. Definition of the reciprocal lattice. So

$$e^{iG.R} = 1$$

and  $\psi(\mathbf{r} + \mathbf{R}) \equiv e^{i\mathbf{k}'.\mathbf{R}} \psi(\mathbf{r})$   $e^{i\mathbf{k}.\mathbf{R}} \equiv e^{i\mathbf{k}'.\mathbf{R}}$

k' is exactly equivalent to k.

The only independent values of k are those in the first Brillouin zone.

# Formation of allowed and forbidden energy bands:

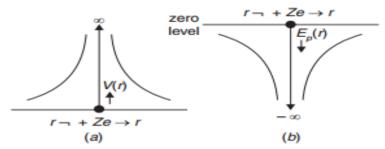

A crystal is a solid consisting of a regular and repetitive arrangement of atoms or molecules (strictly speaking, ions) in space. If the positions of the atoms in the crystal are represented by points, called lattice points, we get a crystal lattice. The distance between the atoms in a crystal is fixed and is termed the lattice constant of the crystal. To discuss the behaviour of electrons in a crystal, we consider an isolated atom of the crystal. If Z is the atomic number, the atomic nucleus has a positive charge Ze. At a distance r from the nucleus, the electrostatic potential due to the nuclear charge is (in SI units)

$$V(r) = \frac{Ze}{4\pi\varepsilon_0 r}$$

where  $\epsilon 0$  is the permittivity of free space. Since an electron carries a negative charge, the potential energy of an electron at a distance r from the nucleus is

$$E_{p}(r) = -eV(r) = -\frac{Ze^{2}}{4\pi\epsilon_{0}r}$$

V(r) is positive while E p(r) is negative. Both V(r) and E p(r) are zero at an infinite distance from the nucleus. Figs. 1.2(a) and (b) show the variation of V(r) and E p(r), respectively with r.

Figure 11: Variation of (a) Potential in the field of a nucleus with distance, (b) Potential energy of an electron with its distance from the nucleus.

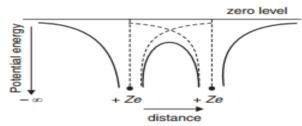

We now consider two identical atoms placed close together. The net potential energy of an electron is obtained as the sum of the potential energies due to the two individual nuclei. In the region between the two nuclei, the net potential energy is clearly smaller than the potential energy for an isolated nucleus shown in the figure 11.

Figure 12: Potential energy variation of an electron with distance between two identical nuclei.

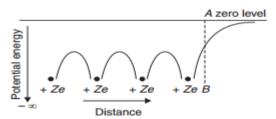

The potential energy along a line through a row of equispaced atomic nuclei, as in a crystal, is diagrammatically shown in Figure 12. The potential energy between the nuclei is found to consist of a series of humps. At the boundary AB of the solid, the potential energy increases and approaches zero at infinity, there being no atoms on the other side of the boundary to bring the curve down.

The total energy of an electron in an atom, kinetic plus potential, is negative and has discrete values. These discrete energy levels in an isolated atom are shown by horizontal lines in Figure. When a number of atoms are brought close together to form a crystal, each atom will exert an electric force on its neighbours. As a result of this interatomic coupling, the crystal forms a single electronic system obeying Pauli's exclusion principle. Therefore, each energy level of the isolated atom splits into as many energy levels as there are atoms in the crystal, so that Pauli's exclusion principle is satisfied. The separation between the split-off energy levels is very small. This large number of discrete and closely spaced energy levels form an energy band. Energy bands are represented schematically by shaded regions in Figure 13.

Figure 13: Potential energy of an electron along a row of atoms in a crystal.

The width of an energy band is determined by the parent energy level of the isolated atom and the atomic spacing in the crystal. The lower energy levels are not greatly affected by the interaction among the neighbouring atoms, and hence form narrow bands. The higher energy levels are greatly affected by the interatomic interactions and produce wide bands. The interatomic spacing, although fixed for a given crystal, is different for different crystals. The width of an energy band thus depends on the type of the crystal, and is larger for a crystal with a small interatomic spacing. The width of a band is independent of the number of atoms in the crystal, but the number of energy levels in a band is equal to the number of atoms in the solid. Consequently, as the number of atoms in the crystal increases, the separation between the

energy levels in a band decreases. As the crystal contains a large number of atoms ( $\approx 1029$  m-3), the spacing between the discrete levels in a band is so small that the band can be treated as continuous.

Figure 14: Splitting of energy levels of isolated atoms into energy bands as these atoms are brought close together to produce a crystal.

The lower energy bands are normally completely filled by the electrons since the electrons always tend to occupy the lowest available energy states. The higher energy bands may be completely empty or may be partly filled by the electrons. Pauli's exclusion principle restricts the number of electrons that a band can accommodate. A partly filled band appears when a partly filled energy level produces an energy band or when a totally filled band and a totally empty band overlap.

As the allowed energy levels of a single atom expand into energy bands in a crystal, the electrons in a crystal cannot have energies in the region between two successive bands. In other words, the energy bands are separated by gaps of forbidden energy.

The average energy of the electrons in the highest occupied band is usually much less than the zero level marked in Fig. 1.5(b). The rise of the potential energy near the surface of the crystal, as shown in Fig. 1.5(b), serves as a barrier preventing the electrons from escaping from the crystal. If sufficient energy is imparted to the electrons by external means, they can overcome the surface potential energy barrier, and come out of the crystal surface.

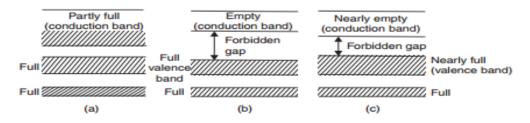

On the basis of the band structure, crystals can be classified into metals, insulators, and semiconductors.

#### Metal:

A crystalline solid is called a metal if the uppermost energy band is partly filled or the uppermost filled band and the next unoccupied band overlap in energy. Here, the electrons in the uppermost band find neighbouring vacant states to move in, and thus behave as free particles. In the presence of an applied electric field, these electrons gain energy from the field and produce an electric current, so that a metal is a good conductor of electricity. The partly filled band is called the conduction band. The electrons in the conduction band are known as free electrons or conduction electrons.

#### **Insulator:**

In some crystalline solids, the forbidden energy gap between the uppermost filled band, called the valence band, and the lowermost empty band, called the conduction band, is very large. In such solids, at ordinary temperatures only a few electrons can acquire enough thermal energy to move from the valence band into the conduction band. Such solids are known as insulators. Since only a few free electrons are available in the conduction band, an insulator is a bad conductor of electricity. Diamond having a forbidden gap of 6 eV is a good example of an insulator. The energy band structure of an insulator is schematically shown in Figure 15.

#### **Semiconductor:**

A material for which the width of the forbidden energy gap between the valence and the conduction band is relatively small (~ 1 eV) is referred to as a semiconductor. Germanium and silicon having forbidden gaps of 0.78 and 1.2 eV, respectively, at 0 K are typical semiconductors. As the forbidden gap is not very wide, some of the valence electrons acquire enough thermal energy to go into the conduction band. These electrons then become free and can move about under the action of an applied electric field. The absence of an electron in the valence band is referred to as a hole. The holes also serve as carriers of electricity. The electrical conductivity of a semiconductor is less than that of a metal but greater than that of an insulator. The band diagram of a semiconductor is given in Figure 15.

Figure 15: Energy band structure of (a) metal, (b) insulator, and (c) semiconductor. [2]

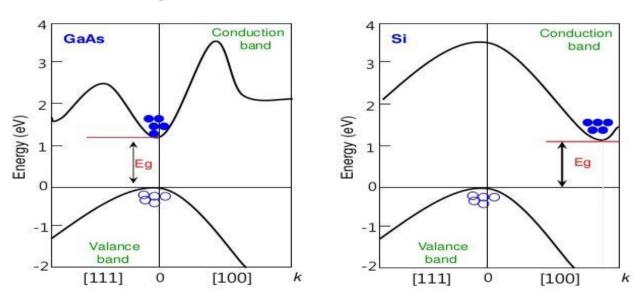

Effective mass, Wave vector, Energy-band (E-k) diagram: Effective mass  $(m^*)$  is the mass that it seems to have when responding to forces or with other identical particles in a thermal distribution. The "wave-particle" motion of electrons in a lattice is not the same as that for a free electron, because of the interaction with the periodic potential of the lattice.

The effective mass is an inverse function of the curvature of the E-k diagram: weak curvature gives large mass, and strong curvature gives small mass.

In general, the effective mass is a tensor quantity, however, for parabolic bands, it is a constant.

Wave vector (k in cm<sup>-1</sup>) is a variable which states the change of the momentum of an electron in different directions or co-ordinates, while the electron traverse from valance band to conduction band and vice versa.

In a typical quantitative calculation of band structures, the wave function of a single electron traveling through a perfectly periodic lattice is assumed to be in the form of a plane wave moving in the x-direction (say) with propagation constant k, also called a *wave vector*.

The wave vector of the electron is much larger than that of the photon.

It is to be expressed thematically in scalar form, p=(kh)/2\*pi, Where p is momentum of electron, h is plunk constant. The momentum changes instantaneously due to the variation of momentum of the electron while travelling through one non-uniform potential barrier.

k = (2\*pi)/wavelength this is the expression illustrates the variation of wave vector, due to the generated wave length by the electron.

The band structure of a crystalline solid, i.e allowed values of energy, while plotted as a function of k, gives energy-momentum (*E-k*) relationship is usually obtained by solving the Schrodinger equation of an approximate one-electron problem. It shows the relationship between the energy and momentum of available quantum mechanical states for electrons in the material.

# Relation between E-K diagram & Effective mass:

Figure 16. Energy-band (E-k) diagram of GaAs and Si

**Debye length:** Debye length is the distance over which significant charge separation can occur, is the measure of a mobile charge carrier's (e.g. electrons) screen out electric fields in plasmas and other conductors.

Debye length (LD), is a characteristic length for semiconductors gives an idea of the limit of the potential change in response to an abrupt change in the doping profile and is defined as,

$$L_D \equiv \sqrt{\frac{\varepsilon_s kT}{q^2 N}} = \sqrt{\frac{\varepsilon_s}{qN\beta_{th}}}.$$

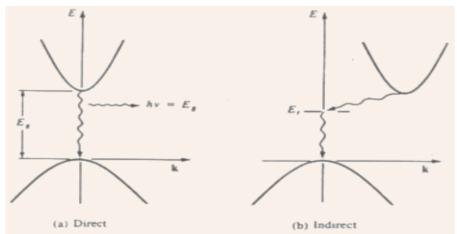

#### **Direct & indirect band-gap semiconductors:**

For a direct-band gap material, the minimum of the conduction band and maximum of the valance band lies at the same momentum, k, values. When an electron sitting at the bottom of the CB recombines with a hole sitting at the top of the VB, there will be no change in momentum values. Energy is conserved by means of emitting a photon, such transitions are called as radiative transitions.

Direct-band gap Semiconductor (e.g. GaAs, InP, AlGaAs)

For an indirect-band gap material the minimum of the CB and maximum of the VB lie at different k-values. When an e-and hole recombine in an indirect-band gap s/c, phonons must be involved to conserve momentum. Indirect-band gap Semiconductor (e.g. Si and Ge).

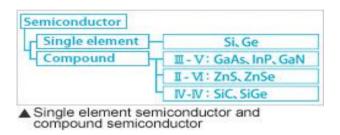

The transition that involves in an indirect band gap Semiconductor phonons without producing photons are called nonradiative (radiationless) transitions, and result in inefficient photon producing. So in order to have efficient LED's and LASER's, one should choose materials having direct band gaps such as compound Semiconductor of GaAs, AlGaAs, etc. compound semiconductor: semiconductor composed composed of two or more elements is called a compound semiconductor. Typical examples of compound semiconductors include gallium arsenide (GaAs), gallium nitride (GaN), indium phosphide (InP), zinc selenide (ZnSe), and silicon carbide (SiC).

#### Charge Carriers in Semiconductors: Intrinsic & extrinsic semiconductor:

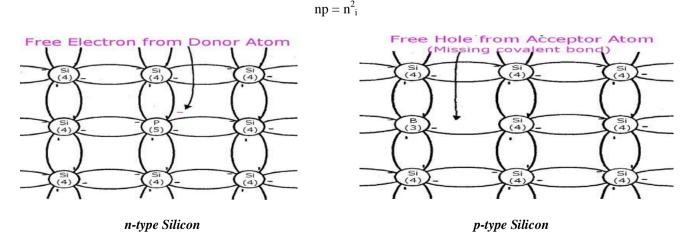

For intrinsic semiconductors at finite temperatures, thermal agitation occurs which results in continuous excitation of electrons from the valence band to the conduction band, and leaving an equal number of holes in the valence band. This process is balanced by recombination of the electrons in the conduction band with holes in the valence band. At steady state, the net result is n = p = ni, where ni is the intrinsic carrier density.

Doping is a method of selectively increasing carrier concentration, by addition of selected impurities to an intrinsic semiconductor. This is called an extrinsic semiconductor. In any semiconductor at equilibrium, the law of mass action should be satisfied i.e.

# Effect of temperature and energy gap on intrinsic concentration, effect of temperature on extrinsic semiconductor

An intrinsic semiconductor several factors come to mind:

- 1. It is extremely pure, containing an insignificant amount of impurities.

- 2. The properties of the material depend only on the element(s) the semiconductor is made of.

- 3. For every electron created, a hole is created also,  $n_o = p_o = n_i$ .

For an electron-hole pair to be created in an intrinsic semiconductor, a bond must be broken in the lattice, and this requires energy. An electron in the valence band must gain enough energy to jump to the conduction band and leave a hole behind. ni represents the intrinsic carrier concentration, or we can see it as the number of bonds broken in an intrinsic semiconductor.

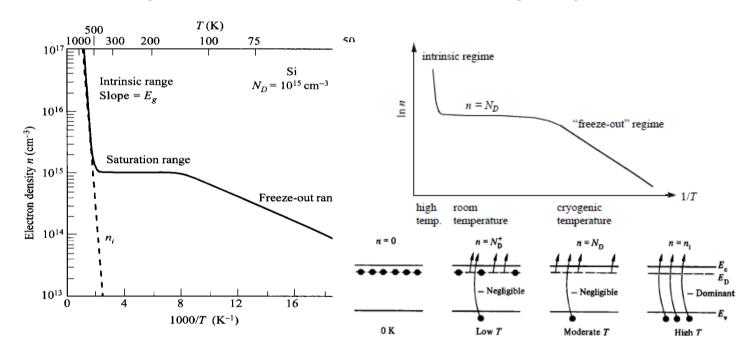

As the temperature is increased, the number of broken bonds (carriers) increases because there is more thermal energy available so more and more electrons gain enough energy to break free. Each electron that makes it to the conduction band leaves behind a hole in the valence band and there is an increase in both the electron and hole concentration. As the temperature is decreased, electrons do not receive enough energy to break a bond and remain in the valence band. If electrons are in the conduction band they will quickly lose energy and fall back to the valence band, annihilating a hole. Therefore, lowering the temperature causes a decrease in the intrinsic carrier concentration, while raising the temperature causes an increase in intrinsic carrier concentration.

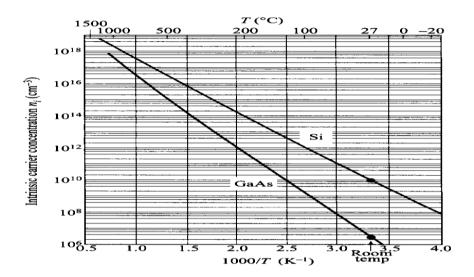

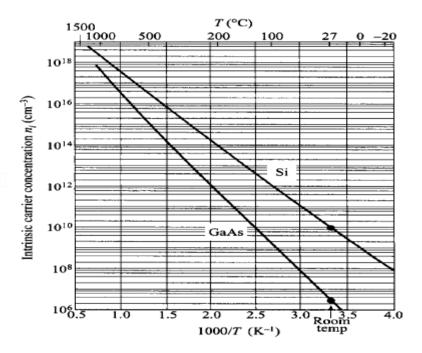

Fig.Intrinsic carrier concentrations of Si and GaAs as a function of reciprocal temperature

Fig. Electron density as a function of temperature for a Si sample with donor impurity concentration of 1015 cm-3

# Basic concept on optical absorption ,photoluminescence, carrier life time , carrier generation and recombination

Whenever the thermal-equilibrium condition of a semiconductor system is disturbed (i.e., pn  $\neq$  n<sub>i</sub>2), processes exist to restore the system to equilibrium (i.e., pn  $\neq$  n<sub>i</sub><sup>2</sup>). These processes are recombination when pn > n' and thermal generation when pn < n<sub>i</sub><sup>2</sup>.

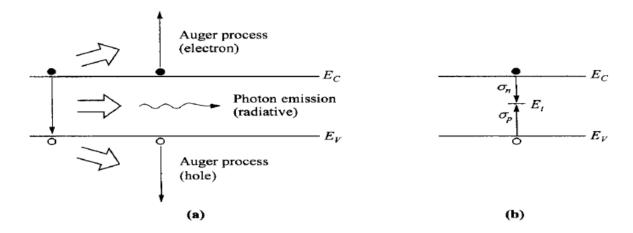

Figure... illustrates the band-to-band electron-hole recombination. The

Energy of an electron in transition from the conduction band to the valence band is conserved by emission of a photon (radiative process) or by transfer of the energy to another free electron or hole (Auger process). The former process is the inverse of direct optical absorption, and the latter is the inverse of impact ionization.

Fig. a),b) Recombination processes (the reverse are generation processes). (a) Band-to-band recombination. Energy is exchanged to a radiative or Auger process. (b) Recombination through single-level traps (nonradiative).

For this type of transition, the recombination rate is proportional to the product of electron and hole concentrations given by

Re = Rec pn.

The term Rec called the recombination coeficient, is related to the thermal generation rate Gth, by

$$R_{ec} = \frac{G_{th}}{n_i^2}.$$

Rec, is a function of temperature and is also dependent on the band structure of the semiconductor.

$$U = R_e - G_{th} = R_{ec}(pn - n_i^2)$$

$$\approx R_{ec} \Delta p N_D = \frac{\Delta p}{\tau_p}$$

where the carrier lifetime for holes

$$\tau_p = \frac{1}{R_{ec}N_D}$$

and in p-type material,

$$\tau_n = \frac{1}{R_{ec}N_A}$$

However, in indirect-bandgap semiconductors such as Si and Ge, the dominant transitions are indirect recombinationlgeneration via bulk traps, of density Nt and energy E, present within the bandgap fig b

## **Continuity equation:**

continuity equations deal with time-dependent phenomena such as low-level injection, generation and recombination. Qualitatively, the net change of carrier concentration is the difference between generation and recombination, plus the net current flowing in and out of the region of interest. The continuity equations are:

$$\frac{\partial n}{\partial t} = G_n - U_n + \frac{1}{q} \nabla \cdot \boldsymbol{J}_n,$$

$$\frac{\partial p}{\partial t} = G_p - U_p - \frac{1}{q} \nabla \cdot \boldsymbol{J}_p$$

where Gn, and Gp are the electron and hole generation rate (Cm-3—S-1) respectively, caused by external influences such as the optical excitation with photons or impact ionization under large electric fields.

# Degeneracy and non-degeneracy of semiconductor:

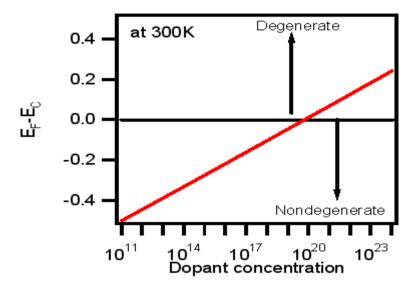

If dopants added at much higher concentrations, dopant atoms come much closer to each other and it is no longer valid to assume the donor levels as atom like. If the inter-atomic distance is closer (typically < 10nm) then the atomic levels turn into bands. This leads to significant changes in the crystal structure as well as the physical properties. Another very important effect is, highly doped semiconductors come to freeze-out at much lower temperatures, meaning the freeze-out region is almost eliminated. Such highly doped semiconductors are called **Degenerate** semiconductors.

It is also to be noted that the donors (or acceptors) energy levels are assumed as atom like. Such assumptions are limited up to to a certain level of dopant concentration and such extrinsic semiconductors are called *non-degenerate* semiconductors. In nondegenerate semiconductors, the doping concentrations are smaller than Nc(the effective density of states in the conduction band) and the Fermi levels are more than several kT below EC.

Non degenerate semiconductors are those which:

- -are lightly doped

- -have less value of electron and hole concentration

- -violate Pauli's exclusion principle

Fig. Effect of dopant (donor) concentration on Fermi level position, with respect to conduction band in silicon.

Carrier Concentration and Fermi Level, Fermi Level shift with doping & temperature, invariance of Fermi level at equilibrium:

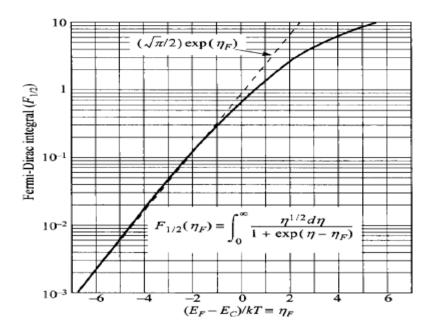

We first consider the intrinsic case without impurities added to the semiconductor. The number of electrons (occupied conduction-band levels) is given by the total  $\,$ number of states  $\,$ N(E)  $\,$ multiplied by the occupancy  $\,$ F(E), integrated over the conduction band,

$$n = \int_{E_C}^{\infty} N(E) F(E) dE$$

The density of states N(E) can be approximated by the density near the bottom of the conduction band for low-enough carrier densities and temperature. The occupancy is a strong function of temperature and energy, and is represented by the Fermi-Dirac distribution Function

$$F(E) = \frac{1}{1 + \exp[(E - E_F)/kT]}$$

Where  $E_F$  is the Fermi energy level which can be determined from the charge neutrality condition

Fig Fermi-Dirac integral  $F_{1/2}$ , as a function of Fermi energy. Dashed line is approximation of Boltzmann statistics.

As shown in the fig for degenerate levels where n- or p-concentrations are near or beyond the effective density of states (Ncor Nv), the value of Fermi-Dirac integral has to be used instead of the simplified Boltzmann statistics.

## **Intrinsic carrier concentration:**

For intrinsic semiconductors at finite temperatures, thermal agitation occurs which results in continuous excitation of electrons from the valence band to the conduction band, and leaving an equal number of holes in the valence band. This process is balanced by recombination of the electrons in the conduction band with holes in the valence band. At steady state, the net result is n = p = ni, where ni is the intrinsic carrier density.

$$E_F = E_i = \frac{E_C + E_V}{2} + \frac{kT}{2} \ln \left( \frac{N_V}{N_C} \right)$$

Hence the Fermi level Ei of an intrinsic semiconductor generally lies very close to, but not exactly at, the middle of the bandgap. The intrinsic carrier density ni can be obtained from

$$n_i = N_C \exp\left(-\frac{E_C - E_i}{kT}\right) = N_V \exp\left(-\frac{E_i - E_V}{kT}\right) = \sqrt{N_C N_V} \exp\left(-\frac{E_g}{2kT}\right)$$

Figure 9 shows the temperature dependence of ni for Si and GaAs. As expected, the larger the bandgap is, the smaller the intrinsic carrier density will be. It also follows that for nondegenerate semiconductors, the product of the majority and minority carrier concentrations is fixed to be.

$$pn = N_C N_V \exp\left(-\frac{E_g}{kT}\right)$$

$$= n_i^2 ,$$

which is known as the mass-action law. But for degenerate semiconductors, pn < ni2; the alternate equations for

n-type materials;

$$n = n_i \exp\left(\frac{E_F - E_i}{kT}\right)$$

or  $E_F - E_i = kT \ln\left(\frac{n}{n_i}\right)$

and for p-type materials;

$$p = n_i \exp\left(\frac{E_i - E_F}{kT}\right)$$

or  $E_i - E_F = kT \ln\left(\frac{p}{n_i}\right)$

Fig.Intrinsic carrier concentrations of Si and GaAs as a function of reciprocal temperature.

# Non-equilibrium condition: Effect of temperature and doping concentration on mobility:

Conductivity of a material is determined by two factors: the concentration of free carriers available to conduct current and their mobility (or freedom to move). In a semiconductor, both mobility and carrier concentration are temperature dependent.

Both increasing temperature and increasing doping levels have the tendency to reduce electron and hole mobility. For temperature, the increased temperature increases the number of phonons, which increases the probability that an electron will be scattered by a phonon. For doping levels, each dopant atom is a defect site that an electron can scatter from.

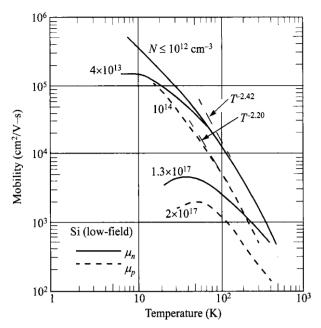

Fig. Mobility of electrons and holes in Si as a function of temperature

#### **Drift & diffusion of carriers:**

The drift current is due to the motion of charge carriers due to the force exerted on them by an electric field.

Whenever there exists a gradient of carrier concentration, a process of diffusion occurs by which the carriers migrate from the region of high concentration toward the region of low concentration, to drive the system toward a state of uniformity. This flow or flux of carriers, taking electrons as an example, is governed by the Fick's law,

The most-common current conduction consists of the drift component, caused by the electric field, and the diffusion component, caused by the carrier-concentration gradient. The current-density equations are:

$$\begin{aligned} \boldsymbol{J}_n &= q \, \mu_n \boldsymbol{n} \mathcal{E} + q \boldsymbol{D}_n \nabla \boldsymbol{n} \\ \boldsymbol{J}_p &= q \, \mu_p \boldsymbol{p} \mathcal{E} - q \boldsymbol{D}_p \nabla \boldsymbol{p} \\ \boldsymbol{J}_{\text{cond}} &= \boldsymbol{J}_n + \boldsymbol{J}_p \,, \end{aligned}$$

where Jn, and Jp are the electron and hole current densities, respectively.

# Hall Effect and piezo electric effect:

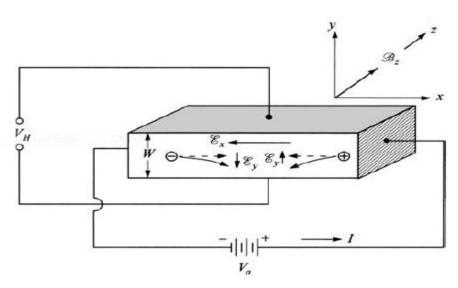

The Hall effect is the generation of a Hall voltage VH, when a piece of semiconductor is biased with a current and placed under a magnetic field that is orthogonal to the current flow. The generated Hall voltage, assuming a Hall factor rH = 1 and a p-type semiconductor, is given by

$V_H = R_H W J_x \mathcal{B} = W \mathcal{E}_x \mu \mathcal{B}$

The Hall effect is used in common practice to measure certain properties of semiconductors: namely, the carrier concentration, mobility, and the type (n or p). It is an important analytical tool since a simple conductance measurement can only give the product of concentration and mobility, and the type remains unknown.

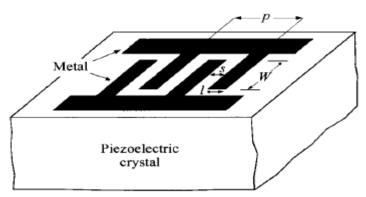

**Piezoelectric Effect** is the ability of certain materials to generate an electric charge in response to applied mechanical stress. The word Piezoelectric is derived from the Greek piezein, which means to squeeze or press, and piezo, which is Greek for "push".

One of the unique characteristics of the piezoelectric effect is that it is reversible, meaning that materials exhibiting the direct piezoelectric effect (the generation of electricity when stress is applied) also exhibit the converse piezoelectric effect (the generation of stress when an electric field is applied).

Common piezoelectric materials are quartz, LiNbO,, ZnO, BaTiO,, LiTaO,, and lead zirconate titanates. These materials are also good insulators. Less common piezoelectric materials are semiconductors such as CdS, CdSe, CdTe, and GaAs. A prerequisite of the piezoelectric effect is some degree of lattice order, so crystal or polycrystal structures are required.

Fig.Interdigital transducer on bulk piezoelectric substrate.

# **Module II: Junction Physics in Semiconductor Devices:**

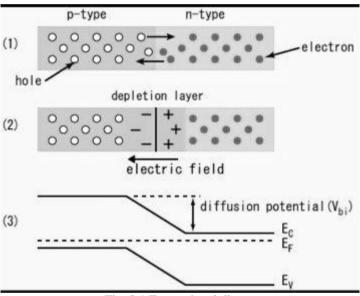

## 2.1 PN Junction Diode:

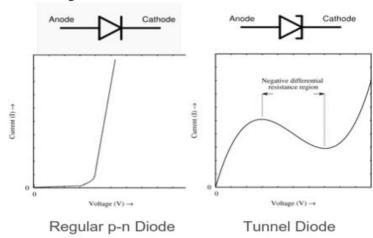

A *PN Junction Diode* is one of the simplest semiconductor devices around, and which has the characteristic of passing current in only one direction only. However, unlike a resistor, a diode does not behave linearly with respect to the applied voltage as the diode has an exponential current-voltage (I-V) relationship and therefore we can not described its operation by simply using an equation such as Ohm's law.

If a suitable positive voltage (forward bias) is applied between the two ends of the PN junction, it can supply free electrons and holes with the extra energy they require to cross the junction as the width of the depletion layer around the PN junction is decreased.

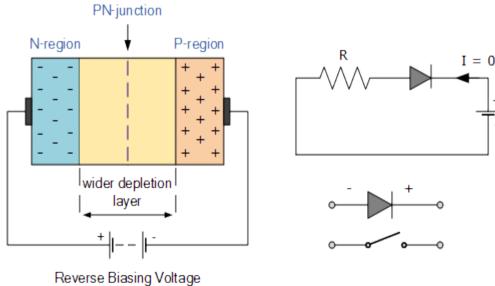

By applying a negative voltage (reverse bias) results in the free charges being pulled away from the junction resulting in the depletion layer width being increased. This has the effect of increasing or decreasing the effective resistance of the junction itself allowing or blocking current flow through the diode.

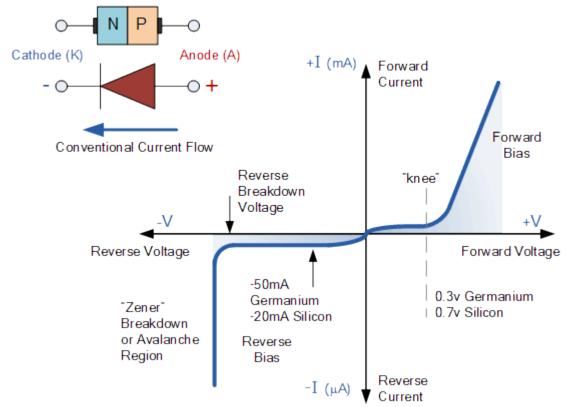

Then the depletion layer widens with an increase in the application of a reverse voltage and narrows with an increase in the application of a forward voltage. This is due to the differences in the electrical properties on the two sides of the PN junction resulting in physical changes taking place. One of the results produces rectification as seen in the PN junction diodes static I-V (current-voltage) characteristics. Rectification is shown by an asymmetrical current flow when the polarity of bias voltage is altered as shown below.

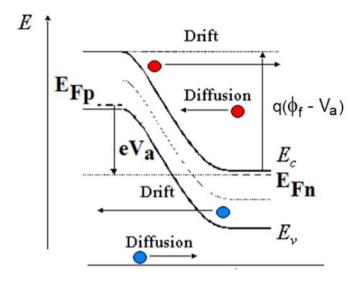

# 2.2 Energy band diagram:

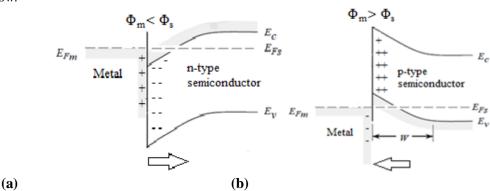

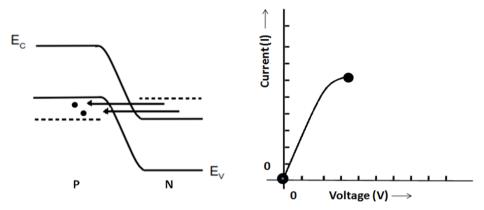

Fig. 2.1 Energy band diagra

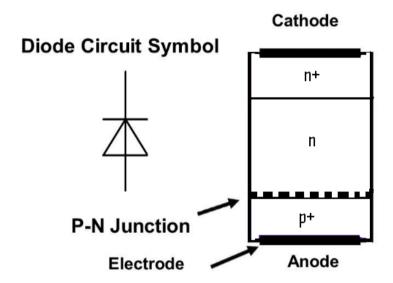

# 2.3 Junction Diode Symbol and Plotting of junction voltage (Static I-V Characteristics)

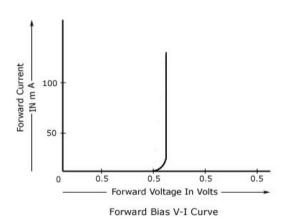

Fig. 2.2 Plotting of junction voltage

But before we can use the PN junction as a practical device or as a rectifying device we need to firstly bias the junction, ie connect a voltage potential across it. On the voltage axis above, "Reverse Bias" refers to an external voltage potential which increases the potential barrier. An external voltage which decreases the potential barrier is said to act in the "Forward Bias" direction.

There are two operating regions and three possible "biasing" conditions for the standard Junction Diode and these are: Zero Bias – No external voltage potential is applied to the PN junction diode.

Reverse Bias – The voltage potential is connected negative, (-ve) to the P-type material and positive, (+ve) to the N-type material across the diode which has the effect of Increasing the PN junction diode's width.

Forward Bias – The voltage potential is connected positive, (+ve) to the P-type material and negative, (-ve) to the N-type material across the diode which has the effect of Decreasing the PN junction diodes width.

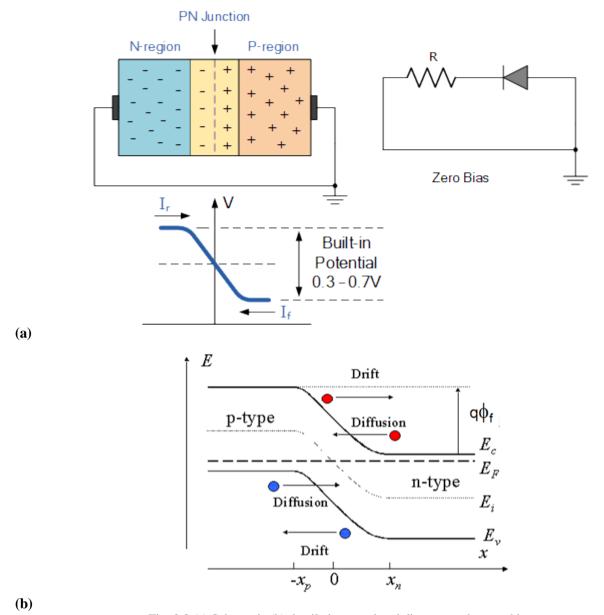

## 2.4 Zero Biased PN Junction Diode

When a diode is connected in a Zero Bias condition, no external potential energy is applied to the PN junction. However if the diodes terminals are shorted together, a few holes (majority carriers) in the P-type material with enough energy to overcome the potential barrier will move across the junction against this barrier potential. This is known as the "Forward Current" and is referenced as IF

Likewise, holes generated in the N-type material (minority carriers), find this situation favourable and move across the junction in the opposite direction. This is known as the "Reverse Current" and is referenced as IR. This transfer of electrons and holes back and forth across the PN junction is known as diffusion, as shown below.

Fig. 2.3 (a) Schematic (b) detailed energy band diagram under zero bias

The potential barrier that now exists discourages the diffusion of any more majority carriers across the junction. However, the potential barrier helps minority carriers (few free electrons in the P-region and few holes in the N-region) to drift across the junction.

Then an "Equilibrium" or balance will be established when the majority carriers are equal and both moving in opposite directions, so that the net result is zero current flowing in the circuit. When this occurs the junction is said to be in a state of "Dynamic Equilibrium".

The minority carriers are constantly generated due to thermal energy so this state of equilibrium can be broken by raising the temperature of the PN junction causing an increase in the generation of minority carriers, thereby resulting in an increase in leakage current but an electric current cannot flow since no circuit has been connected to the PN junction.

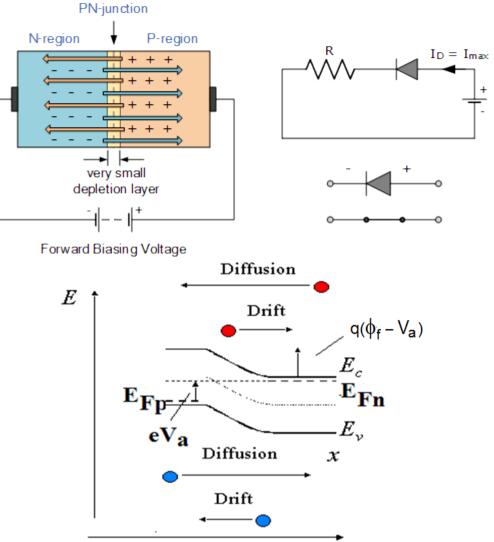

# 2.5 Forward Biased PN Junction Diode

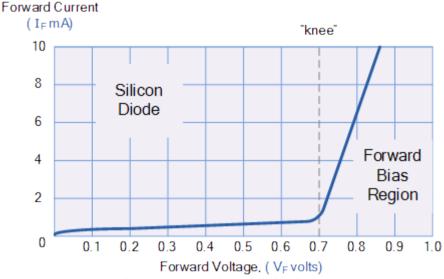

When a diode is connected in a Forward Bias condition, a negative voltage is applied to the N-type material and a positive voltage is applied to the P-type material. If this external voltage becomes greater than the value of the potential barrier, approx. 0.7 volts for silicon and 0.3 volts for germanium, the potential barriers opposition will be overcome and current will start to flow.

This is because the negative voltage pushes or repels electrons towards the junction giving them the energy to cross over and combine with the holes being pushed in the opposite direction towards the junction by the positive voltage. This results in a characteristics curve of zero current flowing up to this voltage point, called the "knee" on the static curves and then a high current flow through the diode with little increase in the external voltage as shown below.

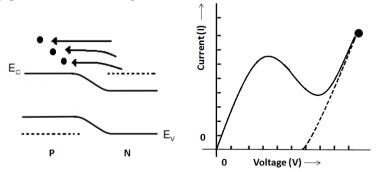

# 2.5.1 Reduction in the Depletion Layer due to Forward Bias current components in forward and reverse biased junction

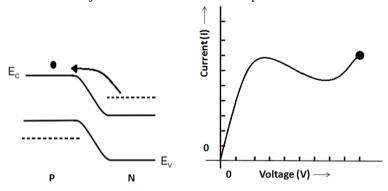

Fig. 2.4 (a) Schematic (b) detailed energy band diagram under positive bias

This condition represents the low resistance path through the PN junction allowing very large currents to flow through the diode with only a small increase in bias voltage. The actual potential difference across the junction or diode is kept constant by the action of the depletion layer at approximately 0.3v for germanium and approximately 0.7v for silicon junction diodes.

Since the diode can conduct "infinite" current above this knee point as it effectively becomes a short circuit, therefore resistors are used in series with the diode to limit its current flow. Exceeding its maximum forward current specification causes the device to dissipate more power in the form of heat than it was designed for resulting in a very quick failure of the device.

# 2.6 Reverse Biased PN Junction Diode

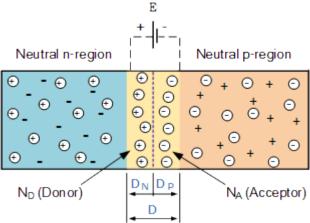

# 2.6.1 Creation of depletion region

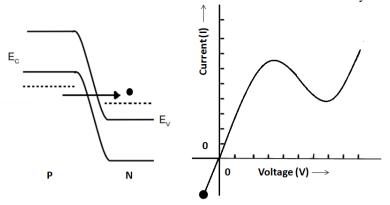

When a diode is connected in a Reverse Bias condition, a positive voltage is applied to the N-type material and a negative voltage is applied to the P-type material.

The positive voltage applied to the N-type material attracts electrons towards the positive electrode and away from the junction, while the holes in the P-type end are also attracted away from the junction towards the negative electrode.

The net result is that the depletion layer grows wider due to a lack of electrons and holes and presents a high impedance path, almost an insulator. The result is that a high potential barrier is created thus preventing current from flowing through the semiconductor material and this potential is called built in potential.

# **2.6.1.1 Built** in potential:

Fig.2.5 Built in potential

As the N-type material has lost electrons and the P-type has lost holes, the N-type material has become positive with respect to the P-type. Then the presence of impurity ions on both sides of the junction cause an electric field to be established across this region with the N-side at a positive voltage relative to the P-side. The problem now is that a free charge requires some extra energy to overcome the barrier that now exists for it to be able to cross the depletion region junction.

This electric field created by the diffusion process has created a "built-in potential difference" across the junction with an open-circuit (zero bias) potential of:

$$E_o = V_T \ln \left( \frac{N_D.N_A}{n_i^2} \right)$$

Where: Eo is the zero bias junction voltage, VT the thermal voltage of 26mV at room temperature, ND and NA are the impurity concentrations and ni is the intrinsic concentration.

A suitable positive voltage (forward bias) applied between the two ends of the PN junction can supply the free electrons and holes with the extra energy. The external voltage required to overcome this potential barrier that now exists is very much dependent upon the type of semiconductor material used and its actual temperature.

Typically at room temperature the voltage across the depletion layer for silicon is about 0.6 - 0.7 volts and for germanium is about 0.3 - 0.35 volts. This potential barrier will always exist even if the device is not connected to any external power source, as seen in diodes.

The significance of this built-in potential across the junction, is that it opposes both the flow of holes and electrons across the junction and is why it is called the potential barrier. In practice, a PN junction is formed within a single crystal of material rather than just simply joining or fusing together two separate pieces.

The result of this process is that the PN junction has rectifying current-voltage (IV or I-V) characteristics. Electrical contacts are fused onto either side of the semiconductor to enable an electrical connection to be made to an external circuit. The resulting electronic device that has been made is commonly called a PN junction Diode or simply Signal Diode

# 2.6.2 Increase in the Depletion Layer due to Reverse Bias

**(b)**

Fig. 2.6 (a) Schematic (b) detailed energy band diagram under negative bias

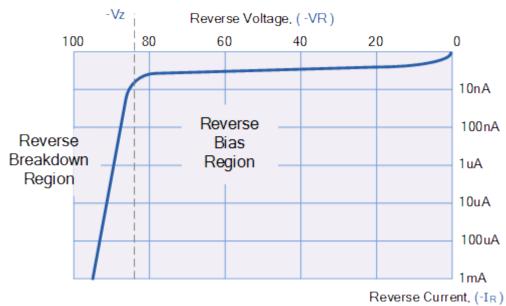

This condition represents a high resistance value to the PN junction and practically zero current flows through the junction diode with an increase in bias voltage. However, a very small leakage current does flow through the junction which can be measured in micro-amperes, ( $\mu A$ ).

One final point, if the reverse bias voltage Vr applied to the diode is increased to a sufficiently high enough value, it will cause the diode's PN junction to overheat and fail due to the avalanche effect around the junction. This may cause the diode to become shorted and will result in the flow of maximum circuit current, and this shown as a step downward slope in the reverse static characteristics curve below.

2.7 Current components in forward and reverse biased junction

2.7.1 Forward Characteristics Curve for a Junction Diode

Fig. 2.7 Forward Characteristics Curve

The application of a forward biasing voltage on the junction diode results in the depletion layer becoming very thin and narrow which represents a low impedance path through the junction thereby allowing high currents to flow. The point at which this sudden increase in current takes place is represented on the static I-V characteristics curve above as the "knee" point.

#### 2.7.2 Reverse Characteristics Curve for a Junction Diode

Fig. 2.8 Reverse Characteristics Curve

Sometimes this avalanche effect has practical applications in voltage stabilising circuits where a series limiting resistor is used with the diode to limit this reverse breakdown current to a preset maximum value thereby producing a fixed voltage output across the diode. These types of diodes are commonly known as Zener Diodes and are discussed in a later tutorial.

# **FAQ**

How electric field strength increases with the reverse bias?

Total voltage across the pn junction will be V+Vx. The electrons at n-side will get pulled from junction region to the terminal region of n-side and similarly the holes at p-side junction will get pulled towards the terminal region of p-side. This results in increasing the depletion region width from its initial length, say 'W' to some 'W+x'. As width of depletion region increases, it results in increasing the electric field strength.

How reverse saturation current occurs and why it exists?

The reverse saturation current is the negligibly small current (in the range of micro amperes) shown in graph, from 0 volts to break down voltage. It remains almost constant (negligible increase do exist) in the range of 0 volts to reverse breakdown voltage. How it occurs? We know, as electrons and holes are pulled away from junction, they dont get diffused each other across the junction. So the net "diffusion current" is zero! What remains is the drift due to electric field. This reverse saturation current is the result of drifting of charge carriers from the junction region to terminal region. This drift is caused by the electric field generated by depletion region.

What happens at reverse breakdown?

At breakdown voltage, the current through diode shoots rapidly. Even for a small change in applied voltage, there is a high increase in net current through the diode. For each pn junction diode, there will be a maximum net current that it can withstand. If the reverse current exceeds this maximum rating, the diode will get damaged.

2.8 Diode Equation

The voltage developed across a p-n junction caused by –

the diffusion of electrons from the n-side of the junction into the p side and

the diffusion of holes from the p side of the junction into the n side

Drift currents only flow when there is an electric field present.

Diffusion currents only flow when there is a concentration difference for either the electrons or holes (or both).

$$egin{align} I_n^{drift} &= qA\mu_n nE \ I_p^{drift} &= qA\mu_p pE \ I^{drift} &= Aqig(\mu_n n + \mu_p pig)E \ \end{array}$$

$$\begin{split} I_n^{diff} &= qAD_n \nabla n = qAD_n \frac{dn}{dx} \\ I_p^{diff} &= -qAD_p \nabla p = -qAD_p \frac{dp}{dx} \\ I_p^{diff} &= I_n^{diff} + I_p^{diff} = qA(D_n \nabla n - D_p \nabla p) \end{split}$$

$$I^T = I^{diff} + I^{drift}$$

#### **Ideal Diodes**

The diode equation gives an expression for the current through a diode as a function of voltage. The *Ideal Diode Law*,

$$I = I_0 \left( e^{\frac{qV}{kT}} - 1 \right)$$

I = the net current flowing through the diode;

$I_0$  = "dark saturation current", the diode leakage current density in the absence of light;

V = applied voltage across the terminals of the diode;

q = absolute value of electron charge;

k = Boltzmann's constant; and

T = absolute temperature (K).

The "dark saturation current"  $(I_0)$  is an extremely important parameter which differentiates one diode from another.  $I_0$  is a measure of the recombination in a device. A diode with a larger recombination will have a larger I<sub>0</sub>. An excellent discussion of the recombination parameter is in [1]

Note that:

- $I_0$  increases as T increases; and

- $I_0$  decreases as material quality increases.

At 300K, kT/q = 25.85 mV, the "thermal voltage".

Lp = diffusion length of holes (cm)

Dp = diffusion constant (cm2/s) L p Lp = average carrier life time (s)

Firstly, we find  $\Delta p$  where  $\Delta p$  is the minority carrier concentration at the edge of the depletion region (DP) we know that the built-in voltage is given by  $V_{bi} = k T/q \ln (N_A N_D n_i^2) V_{bi} = k T/q \ln (N_A N_D n_i^2)$ Applying the law of mass action  $n_i^2 = n_{no} \times p_{no}$

$we \ get \ V_{b\,i} = k \ T/\ q \ ln \ (\ n_{\,n\,o} \ p_{\,n\,o} \ n \ i \ 2 \ ) \ Vbi = \bar{k} T q ln \ (nnopnoni2) \ Rearranging \ p \ o = p \ n \ o \ exp \ (\ q \ V \ b \ i \ k \ T \ )$ ppo=pnoexp[70](qVbikT) => eqn.1 For non-equilibrium situation, i.e. when there's forward bias voltage V f Vf p p (0) = p  $n(0) \exp(q(Vbi-Vf)kT) = \exp(q(Vbi-Vf)kT) = \exp(q(Vbi-Vf)kT) = \exp(q(Vbi-Vf)kT)$ ppo=pnoexp $\stackrel{\text{\tiny ind}}{=}$ (qVkT) where V = V b i - V f V=Vbi-Vf assuming low injection level, i.e. p p  $\approx$  p p o pp $\approx$ ppo eqn.1/eqn.2 by doing this we get  $\Delta p \Delta p$  therefore  $\Delta p = p n o \exp(q V k T - 1) \Delta p = p n o \exp((q V k T - 1))$  Using the continuity equation, we get an expression for the current density J p (x) = q D p L p  $\delta$  p (x) Jp(x)=qDpLp $\delta$ p(x) since  $\Delta$  p =  $\delta$  p (x = 0 )  $\Delta p = \delta p(x=0)$  so  $\delta p(x=0) = p \text{ n o exp}(q \text{ V k T} - 1) \delta p(x=0) = p \text{noexp}(q \text{ V kT} - 1) \text{ J } p(x) = q \text{ D } p \text{ p n o L p exp}(q \text{ V kT} - 1) \text{ J } p(x) = q \text{ D } p \text{ p n o L p exp}(q \text{ V kT} - 1) \text{ J } p(x) = q \text{ D } p \text{ p n o L p exp}(q \text{ V kT} - 1) \text{ J } p(x) = q \text{ D } p \text{ p n o L p exp}(q \text{ V kT} - 1) \text{ J } p(x) = q \text{ D } p \text{ p n o L p exp}(q \text{ V kT} - 1) \text{ J } p(x) = q \text{ D } p \text{ p n o L p exp}(q \text{ V kT} - 1) \text{ J } p(x) = q \text{ D } p \text{$ q V k T - 1) Jp(x) = qDppnoLpexp = (qVkT-1) Doing the same with electrons, we get a similar expression, hence J t o t a  $l = J p + J n = J s \exp(q V k T - 1)$  Jtotal=Jp+Jn=Jsexp(qVkT-1) This is the standard way of expressing the diode equation. However, if we multiply the above expression by the cross-section area, we get the current I.

Fig. 2.9 Symbol of Varactor Diode

Varactor Diode is a reverse biased p-n junction diode, whose capacitance can be varied electrically. As a result these diodes are also referred to as varicaps, tuning diodes, voltage variable capacitor diodes, parametric diodes and variable capacitor diodes. It is well known that the operation of the p-n junction depends on the bias applied which can be either forward or reverse in characteristic. It is also observed that the span of the depletion region in the p-n junction decreases as the voltage increases in case of forward bias. On the other hand, the width of the depletion region is seen to increase with an increase in the applied voltage for the reverse bias scenario. Under such condition, the p-n junction can be considered to be analogous to a capacitor (Figure 1) where the p and n layers represent the two plates of the capacitor

while the depletion region acts as a dielectric separating them. Thus one can apply the formula used to compute the capacitance of a parallel plate capacitor even to the varactor diode.

Hence, mathematical expression for the capacitance of varactor diode is given by:

Where, Cj is the total capacitance of the junction.  $\epsilon$  is the permittivity of the semiconductor material. A is the cross-sectional area of the junction. d is the width of the depletion region. Further the relationship between the capacitance and

the reverse bias voltage is given as Where, Cj is the capacitance of the varactor diode. C is the capacitance of the varactor diode when unbiased. K is the constant, often considered to be 1. Vb is the barrier potential. VR is the applied reverse voltage. m is the material dependent constant. its symbol is shown by Figure 2.9. They are used in

- 1. Tuning circuits to replace the old style variable capacitor tuning of FM radio

- 2. Small remote control circuits

- 3. Tank circuits of receiver or transmitter for auto-tuning as in case of TV

- 4. Signal modulation and demodulation.

- 5. Microwave frequency multipliers as a component of LC resonant circuit

- 6. Very low noise microwave parametric amplifiers

- 7. AFC circuits

- 8. Adjusting bridge circuits

- 9. Adjustable bandpass filters

- 10. Voltage Controlled Oscillators (VCOs)

- 11. RF phase shifters

- 12. Frequency multipliers

# Zener break down principle:

Zener diode is a PN junction diode specially designed to operate in the reverse biased mode. In forward bias mode it acts as normal diode. It has a particular voltage known as Break down voltage, at which the diode breaks down while reverse biased. In the case of normal diodes, the diode damages at the break down voltage.

The basic principle of zener diode is the zener break down. When a diode is heavily doped, it's depletion region will be narrow. When a high reverse voltage is applied across the junction, there will be very strong electric field at the junction. And the electron hole pair generation takes place . Thus heavy current flows. This is known as zener breakdown.

Zener diodes are widely used as voltage references and as shunt regulators to regulate the voltage across small circuits.

The Zener Breakdown is observed in the Zener diodes having Vz less than 5V or between 5 to 8 volts. When a reverse voltage is applied to a Zener diode, it causes a very intense electric field to appear across a narrow depletion region. Such an intense electric field is strong enough to pull some of the valence electrons into the conduction band by breaking their covalent bonds .these electrons then become free electrons which are available for conduction. A large number of such free electrons will constitute a large reverse current through the Zener diode and breakdown is said to have occurred due to the Zener effect.

Dynamic resistance of Zener Diode:

Dynamic Resistance is a concept of resistance used in PN junction in Electronics. Dynamic resistance refers to the change in current in response to a change in voltage at a specific region of the VI curve.

Effect of temperature on Zener Diode:

If a Zener diode is connected to a constant current source, then at constant ambient temperature, the Zener voltage changes and approaches asymptotically a final value. This voltage change is due to the power dissipated in the junction which in turn causes a rise in junction temperature. Zener diodes with a negative temperature coefficient exhibit a Zener voltage reduction, whereas those with a positive temperature coefficient show a Zener voltage increase on application of current. The magnitude of this voltage change due to intrinsic heat generation can be derived from the relevant curves. Because it is not practical to wait during tests until each device has r eached its thermal equilibrium, it is

common practice to measure the breakdown voltage of Zener diodes by application of a pulsating current of less than 1 sec duration. Under these conditions the junction temperature is the same as the ambient temperature. The magnitude of the test current used varies from type to type and is quoted in the relevant data sheets Therefore, designers, but especially customers carrying out acceptance tests, should allow for the fact that the Zener voltage of a device which is at thermal equi- librium will differ from that q uoted in the da

ta sheet. To arrive at an estimate of the equilibrium Zener voltage, a voltage equal to the product of Zener current and thermal differential resistance should be added to the voltage associated with the chosen current as derived from the published dynamically measured breakdown curves.

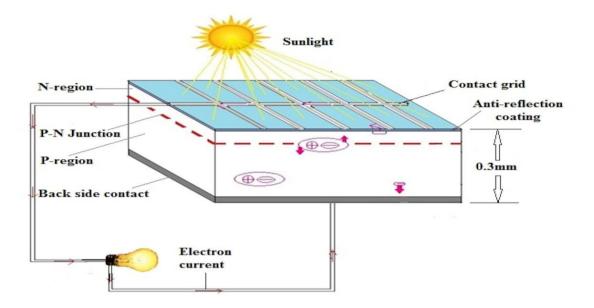

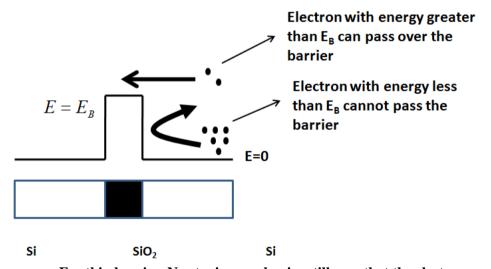

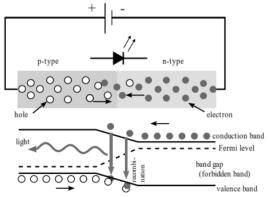

# **Solar Cell:**

Interaction among electrons, holes, phonons, photons and other particles are required to satisfy conservation of energy and crystal momentum. A photon with an energy near a semiconductor band gap has almost zero momentum. An important process is called radiative recombination, where an electron in the conduction band annihilates a hole in the valance band, releasing the excess energy as a photon. If the electron is at the bottom of the conduction band and the hole is at the top of the valence band then in case of direct band gap semiconductor this radiative recombination is a preferred phenomenon. In case of indirect band gap semiconductor, it is not possible as it violets the conservation of crystal momentum. Though it might be possible for indirect band gap material if the process involve the absorption or emission of phonon. In that case the phonon momentum must be equals to the difference between the electron and hole momentum. The involvement of phonon makes the process slower for indirect band gap semiconductor.

Light absorption is just the reverse process of radiative recombination.

When light energy of a particular wavelength equivalent to the band gap absorption edge is incident on an indirect band gap semiconductor, it can penetrate much further than in a direct band gap semiconductor before being absorbed.

This is the key factor for photovoltaic devices. That's why still silicon is used as solar cell substrate material though it is an indirect band gap semiconductor.

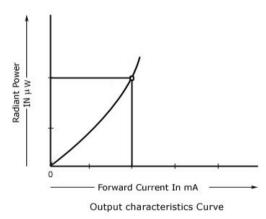

Photoelectric devices convert light energy directly into electrical energy. These devices are self-generating that means it requires no external power source to deliver the output. Photovoltaic and photoluminescence effect are just reverse to each other.

Devices that converts electricity to light exploiting the photoluminescence effect are called emitters (as it emit light) whereas devices that convert light into electricity are called photovoltaic effect. Photovoltaic devices include photoemmisive (non-solid state) devices and photodetectors (solid state devices).

Electrons are in the higher energy state on the n side whereas holes are in the lower energy band on the p side. When these electrons-holes recombine, some of this energy is given up in the form of heat and light. Generally, compound semiconductors (GaAs, GaP, GaAsP etc.) response by releasing greater percentage of energy in the form of light. If the semiconductor material is translucent, the light is emitted and the junction becomes a light source. On the other hand, when light energy of a particular wavelength equivalent to the band gap absorption edge and of particular intensity is incident on a semiconductor, the light is absorbed and breaks the covalent bond to generate electron hole pairs. These carriers cross the junction and generate electric current known as photocurrent flowing through the external circuit.

1. Physics of photovoltaic:

Solar cell is the most popular photovoltaic devices that combine optics with electronics. It converts solar energy into optical energy and also known as solar energy converter. The reaching the earth surface from the sun is basically an electromagnetic radiation which covers a spectral range of 0.2 to 0.3 micrometer.

In 1954, solar cell was first developed by Chaplin, Fuller and Pearson and since then it has shown remarkable progress in the market.

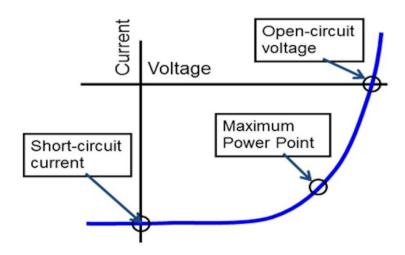

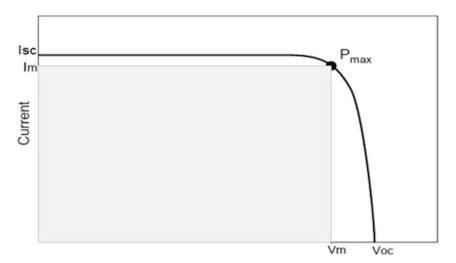

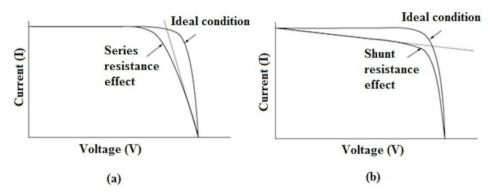

There are two parameters that ultimately used to characterize the solar cell:

- Short circuit current: the maximum current, at zero voltage. Ideally, if V = 0, Isc = IL. Note that Isc is directly proportional to the available sunlight.

- ii) Open circuit voltage: the maximum voltage, at zero current. The value of Voc increases logarithmically with increased sunlight. This characteristic makes solar cells ideally suited to battery charging.

Figure 1: Solar cell device structure

#### Points to remember:

- i) Photon is absorbed and energy is given to an electron in the crystal lattice.

- ii) Generated free electrons-hole pair flow through the materials to produce electricity.

- iii) Different PV materials have different band gap energies.

- iv) Photons with energy equal to the band gap energy are absorbed to create free electrons.

- v) Photons with less energy than the band gap energy pass through the material.

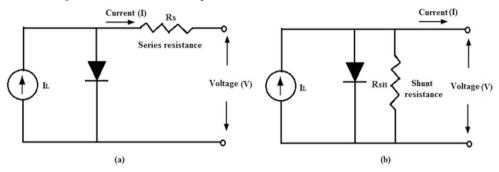

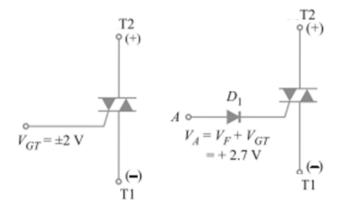

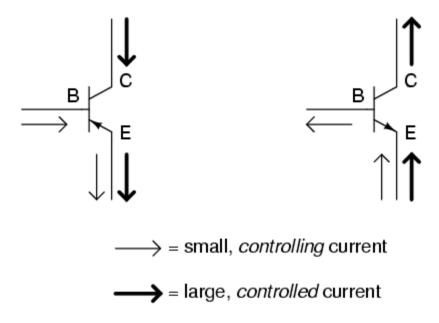

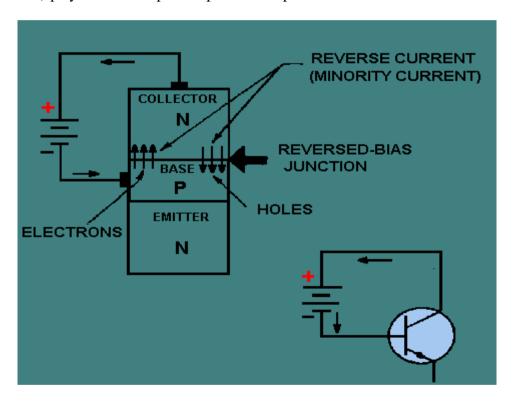

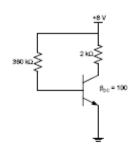

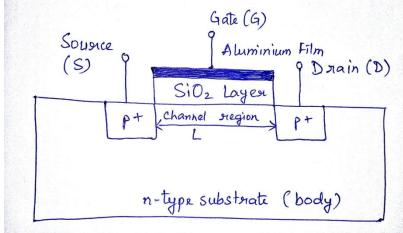

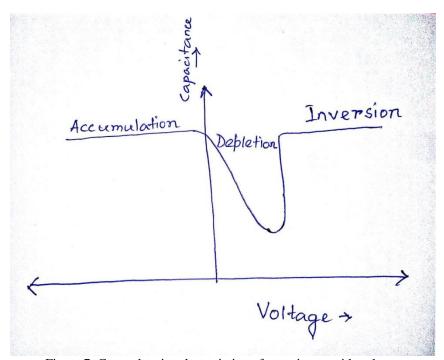

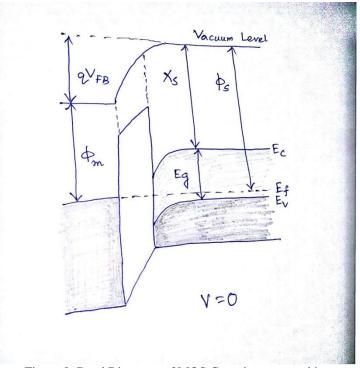

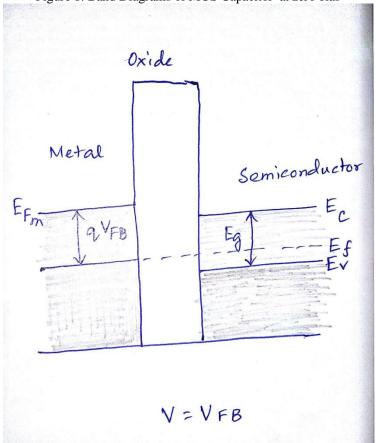

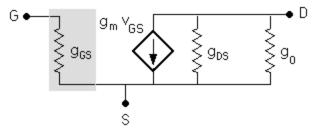

#### 2. Electrical characteristics of solar cell